级对比表半导体用不锈钢管半导体管路

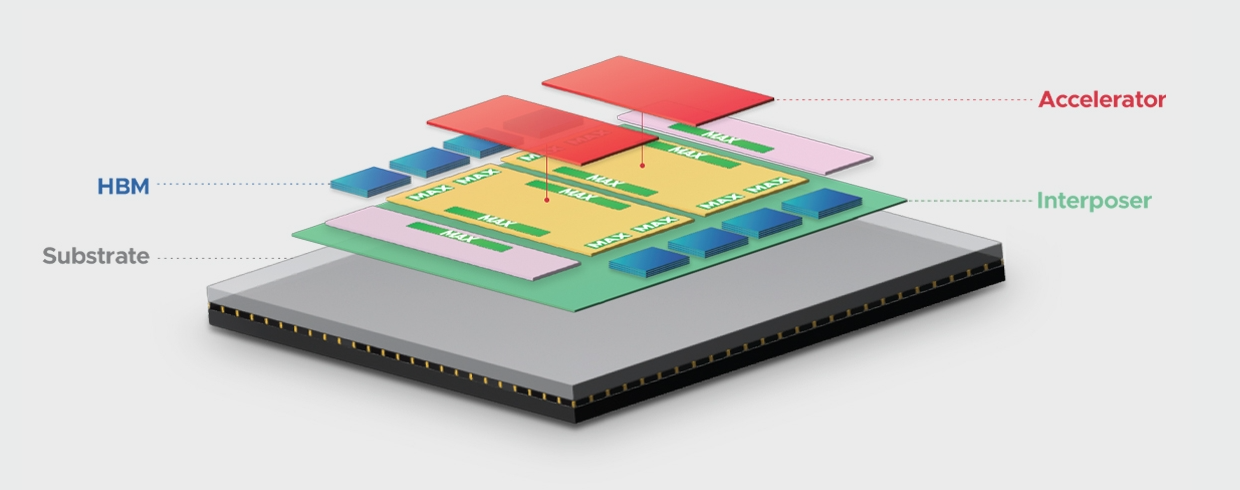

。3.5D XDSiP的最大亮点,正在于可能将超越6000平方毫米的3D堆叠硅晶片和12个HBM模块集成到一个编造级封装中。这是什么观念?

目前手机搬动端的旗舰收拾器骁龙8Elite重心面积是124.1平方毫米;英伟达H200重心面积1526平方毫米;本年英伟达推出的首款Blackwell架构GPUB200,采用双die合封,重心面积也到达1600平方毫米独揽。也即是说博通的3.5D XDSiP平台,可能增援近4个B200重心集成正在一个封装中。

跟着摩尔定律的进一步减缓,优秀封装正在大周围筹划集群中XPU上的运用一经成为了业界共鸣,正在AI筹划中,XPU必要筹划、内存、I/O等功用的庞大集成,以最大范围地低落功耗和本钱。

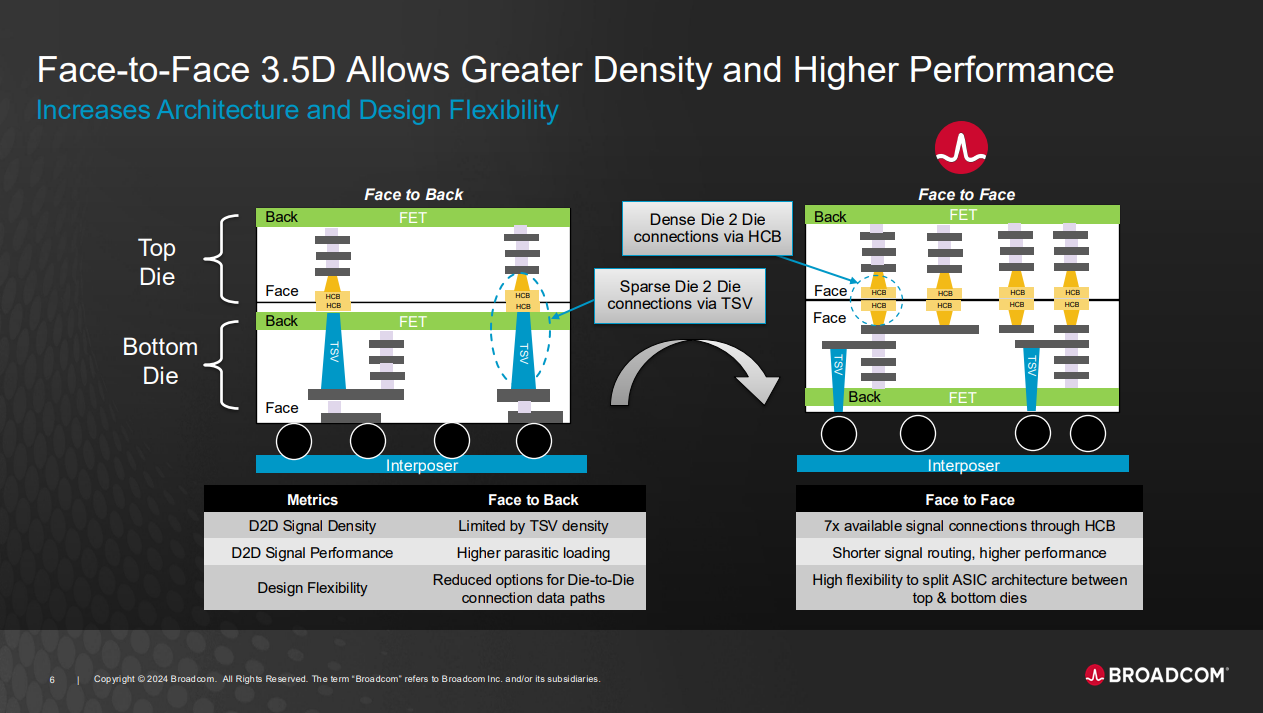

巩固的互连密度:与守旧采用硅通孔TVS的F2B(面到背)的本领比拟,3.5D XDSiP采用HCB(搀和铜键合)以F2F(面临面)的办法将逻辑芯片堆叠,堆叠芯片之间的信号密度降低了7倍;

这项封装本领是博通与台积电多年合营的收获,博通ASIC产物部高级副总裁兼总司理Frank Ostojic默示:“跟着咱们到达摩尔定律的极限,优秀封装对付下一代XPU集群至合紧张。通过与咱们的客户密符合营,咱们正在台积电和EDA合营伙伴的本领和用具底子上创修了一个3.5D XDSiP平台。通过笔直堆叠芯片组件,Broadcom的3.5D平台使芯片策画师或许为每个组件配对确切的修筑工艺,同时缩幼插入器和封装尺寸,从而明显降低职能、效用和本钱。”

台积电营业兴盛高级副总裁张晓强博士默示,台积电和博通正在过去几年中密符合营,将台积电最优秀的逻辑收拾和3D芯片堆叠本领与博通的策画专业常识勾结正在一齐。

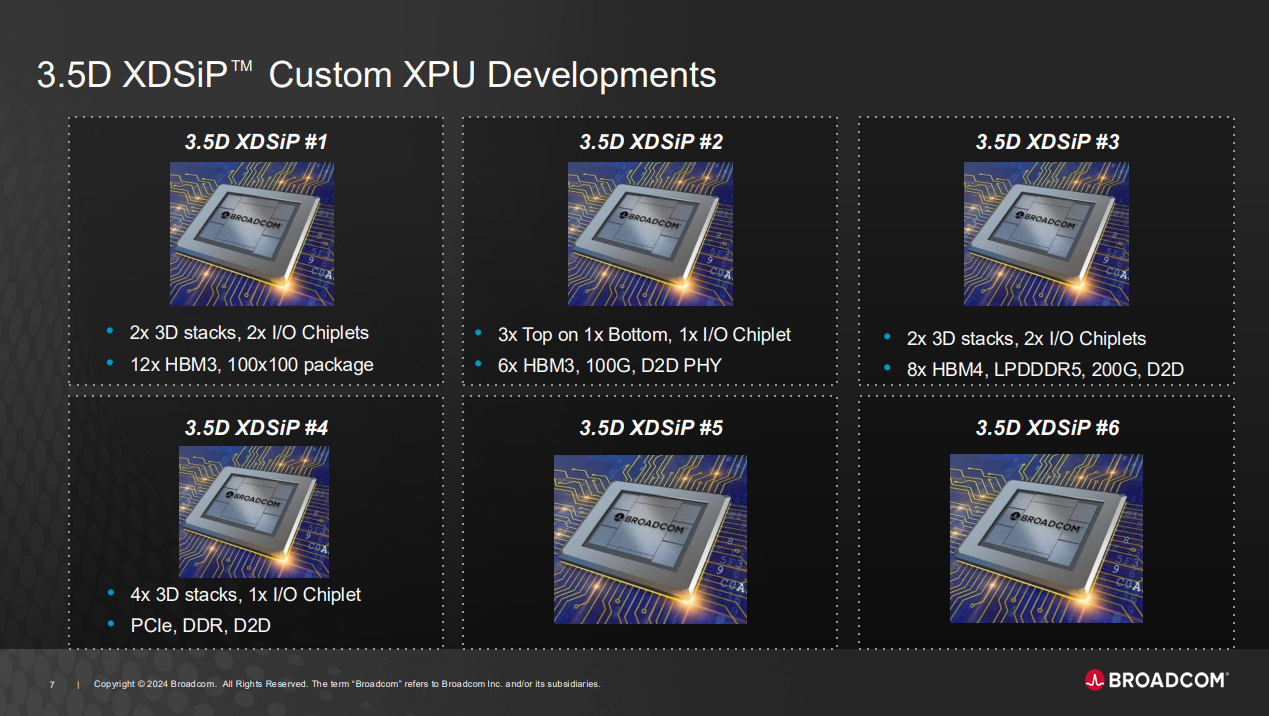

博通默示,3.5D XDSiP本领目前一经被重要的AI规模客户行使,一经有6款产物正正在开辟中。个中富士通下一代2nm造程的Arm收拾器FUJITSU-MONAKA一经确认行使博通3.5D XDSiP本领,这款收拾器面向数据中央、边沿筹划等运用,据此前富士通的先容,MONAKA每颗CPU包罗一个中间的I/O die和四个3D笔直堆叠die,并集成SRAM,估计2027年出货。

优秀封装行为异日AI筹划芯片的紧张片面,博通这种大面积的芯片封装计划,或许极大水平上降低编造集成度,同时通过立异的互连计划,降低片内互连的带宽和降低能效,希望成为异日高职能收拾器的一个紧张偏向。

来了(上) /

来了(下) /

射频开合的独白 /

?它有哪些上风? /

端已于第二季度下旬正式进入量产阶段,预示着该产物将正在第三季度后迎来大批交付。然而,英伟达Blackwell

个8位微收拾器,也是您现正在恐怕正正在行使的x86收拾器系列的祖宗。我找不到8008的好的Die照片,因此我翻开了